## KOTO CDT Module Status Report

Mircea Bogdan The University of Chicago

10/13/2016

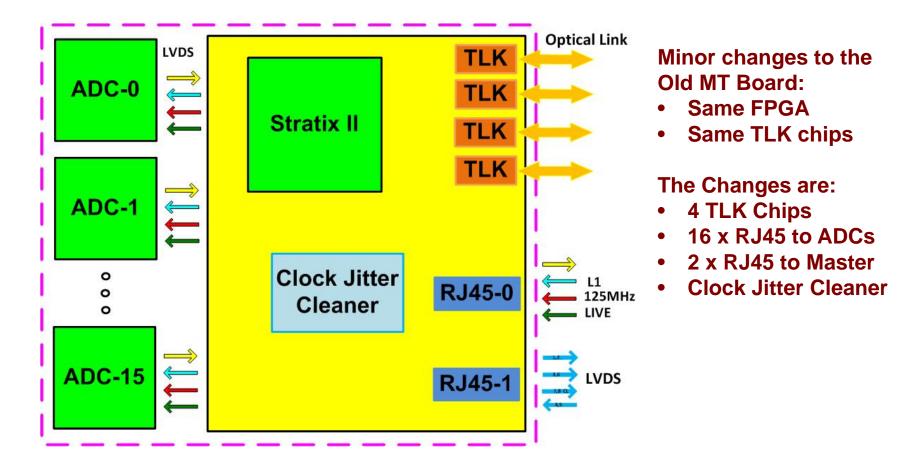

## New CDT - Block Diagram - 8/27/2016

- 1:16 Fan Out Card for LIVE, 125MHz Clock, L1A.

- Service all 16 ADCs in the Crate

- 6U VME Double Width

## New CDT Module Features 8/27/2016

- 1 to 16 Fan-Out Module for 125MHz Clock, LIVE, L1A;

- Replaces the Fan-Out Crate with Modules placed in the ADC Crates;

- Jitter Cleaner: better signal integrity;

- Fully Compatible with Existing and Future (ATCA based) L2 System;

- Doesn't Require any Change in L2 Firmware or Hardware.

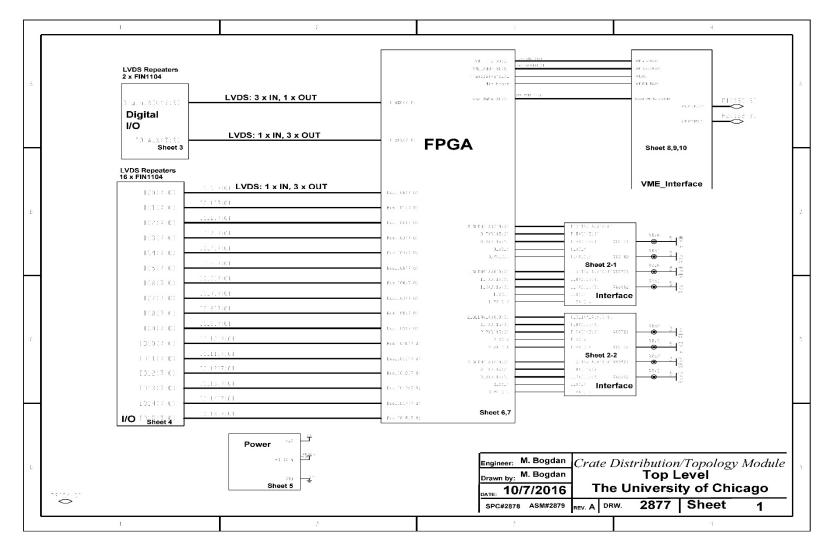

## **New CDT - Block Diagram**

#### **Schematic Finished:**

http://edg.uchicago.edu/~bogdan/KOTO\_Crate\_Distribution\_Module/schematics.html

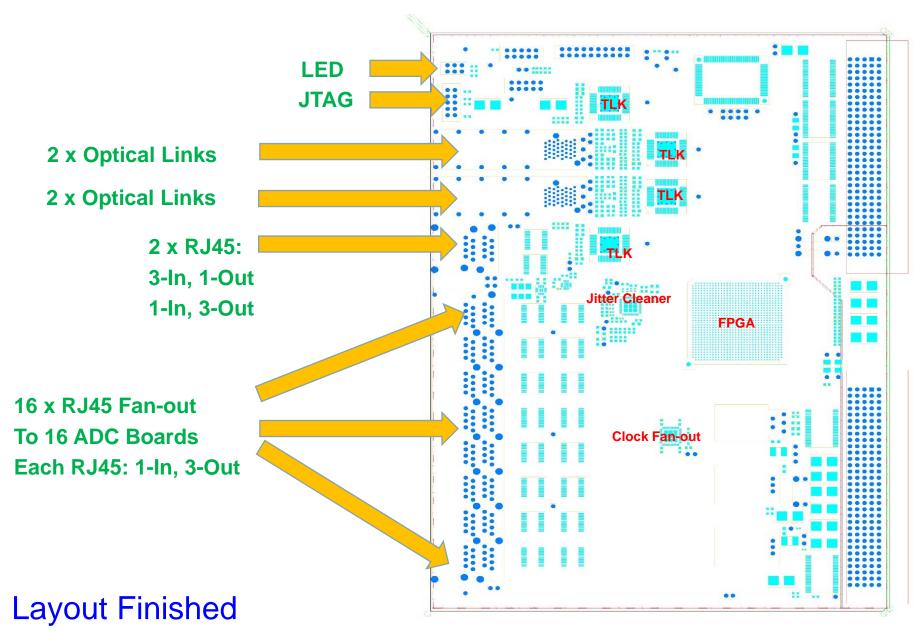

## New CDT – Layout: 6U-Double Width

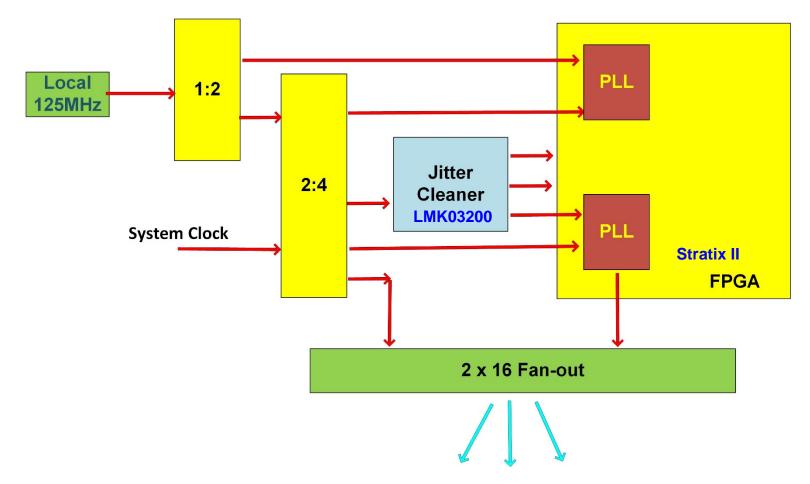

#### **CDT Module – Internal Clock Structure**

Combinations of System and Local Clocks are possible; Clock applied to all FPGA sides will allow future firmware developments.

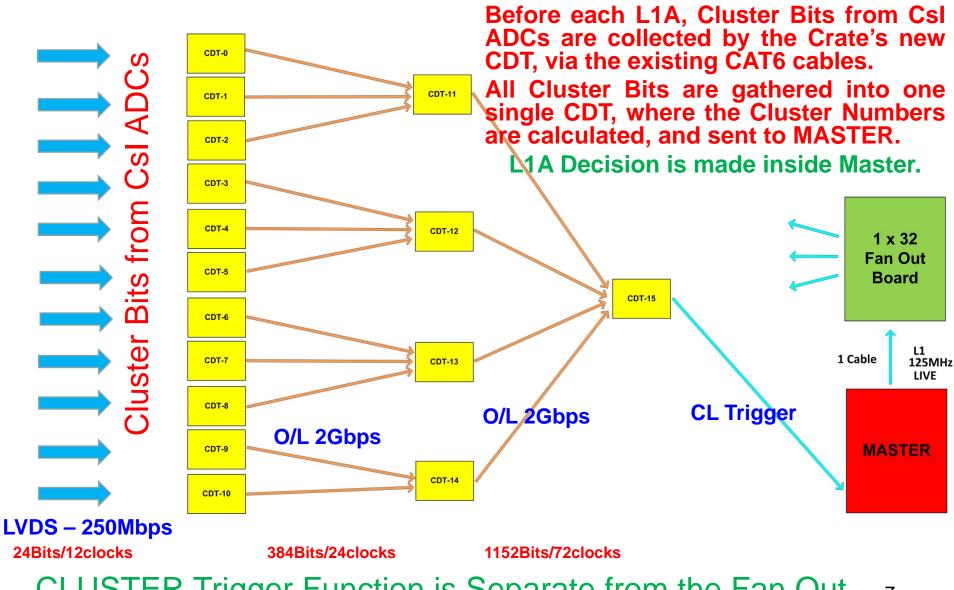

#### CLUSTER Trigger with the new CDT Module 8/27/2016

CLUSTER Trigger Function is Separate from the Fan Out 7

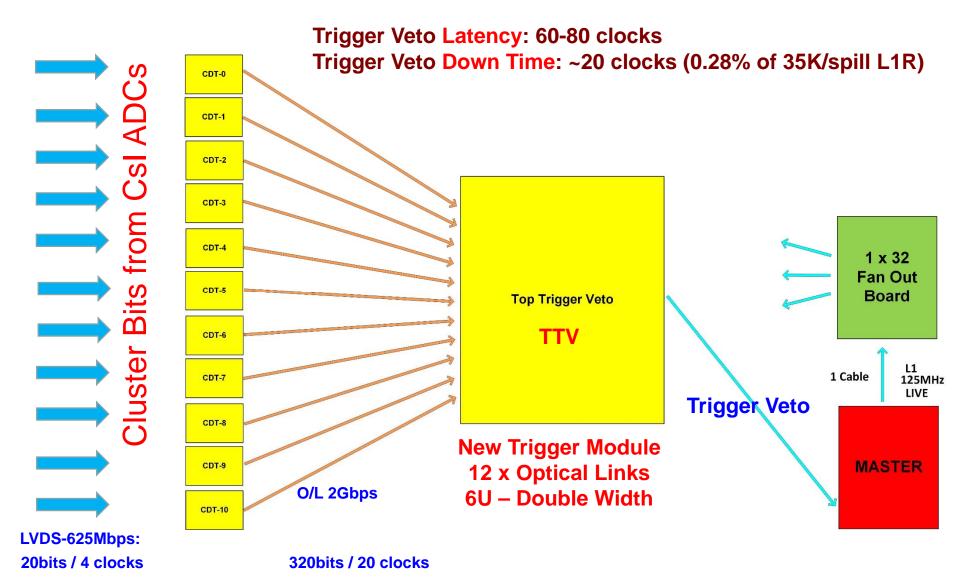

### CLUSTER Trigger with the new CDT Module 10/13/2016

## **How Cluster Trigger Works**

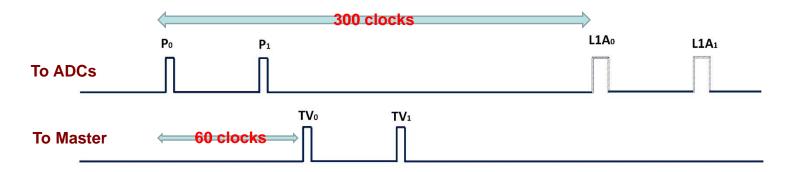

- A Shorter Pre-L1A pulse is sent to ADCs, 300 clocks before the actual L1A pulse;

- ADCs calculate the Cluster Bits (one bit per channel);

- Cluster Bits are sent from ADCs to CDTs via RJ45-LVDS Output;

- All Cluster Bits are collected into Top Trigger Veto Module(TTV);

- TTV sends Cluster Numbers to Master, along with a Trigger Veto (TV) pulse;

- Master uses Cluster Numbers to issue L1A.

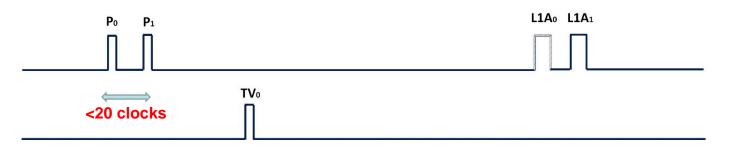

If two Pre-L1A pulses come within 20 clocks, the 2<sup>nd</sup> one is ignored and the corresponding L1A pulse is generated without Trigger Veto. No Data is discarded.

# **KOTO CDT Module**

Questions

Comments

Conclusions